| PC | プログラムカウンタ10ビット |

| Wレジスタ | 回数を数える8ビットのレジスタ |

| Cフラグ | 接続状態かどうかを示す1ビットのレジスタ |

| Tカウンタ | USBのタイミングを取るための3ビットのカウンタ |

| タイマー | 1mSを作る14ビットのカウンタ |

| NOP | ノーオペレーション |

| LDI cc | Wレジスタに8ビット定数をロード |

| START | D-が0になるまで待ち、Tカウンタをクリアする |

| OUT0 | Tカウンタが0になるまで待ち、D+,D-共に0を出力する |

| OUT1 | Tカウンタが0になるまで待ち、D+に1を、D-に0を出力する |

| OUT2 | Tカウンタが0になるまで待ち、D+に0を、D-に1を出力する |

| HIZ | Tカウンタが0になるまで待ち、D+,D-をHi-Zにする |

| BZ aa | D-が0ならジャンプ |

| DJNZ aa | Wレジスタをデクリメントし、0でなければジャンプ |

| BNAK aa | 直前のレスポンスがNAK/STALLならジャンプ |

| BC aa | Cフラグが1ならジャンプ |

| TOGGLE | Cフラグをトグル |

| WAIT | 1mSのタイミングまで待つ |

| IN | Tカウンタがサンプリングタイミングになるまで待つ。D+,D-共に0なら次の命令へ。 そうでなければ、Wレジスタをデクリメントして0なら次の命令へ。 |

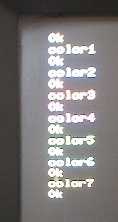

| 色番号 | U | V |

| 0 | 0.000 | 0.000 |

| 1 | 0.500 | -0.081 |

| 2 | -0.168 | 0.5000 |

| 3 | 0.332 | 0.419 |

| 4 | -0.332 | -0.419 |

| 5 | 0.168 | -0.500 |

| 6 | -0.500 | 0.081 |

| 7 | 0.000 | 0.000 |

| 色番号 | U | V |

| 0 | 0.000 | 0.000 |

| 1 | 6.000 | -0.972 |

| 2 | -2.016 | 6.000 |

| 3 | 3.984 | 5.028 |

| 4 | -3.984 | -5.028 |

| 5 | 2.016 | -6.000 |

| 6 | -6.000 | 0.972 |

| 7 | 0.000 | 0.000 |

| files | ファイル一覧 |

| load | ファイルをロード |

| save | ファイルをセーブ |

| kill | ファイルを消去 |

| ヘッダ | 16バイト |

| BASIC | Nbバイト |

| マシン語 | Nmバイト |

| 実行アドレス | 2バイト(ビッグエンディアン) |

| BASICの長さ(Nb) | 2バイト(〃) |

| マシン語の先頭番地 | 2バイト(〃) |

| マシン語の長さ(Nm) | 2バイト(〃) |

| パッド | 8バイト |